低質量切割也有接觸切割,切割法檢測涂層附著力但輸出電流為A)以下,對外界的高頻干擾大,所以有些逆變等離子沒有高頻。雖然是引弧,但外部干擾略小。就這樣。。等離子刻蝕技術在芯片集成電路制造中的應用:等離子刻蝕是芯片集成電路制造中的重要工藝之一。其目的是將掩模圖案完美??地復制到硅片表面,其范圍覆蓋前端。柵極尺寸 CMOS 控制,以及后端金屬鋁蝕刻以及通孔和溝槽蝕刻。今天的集成電路芯片離不開等離子刻蝕技術。

.jpg)

IC作為IC封裝產品之一,切割法檢測附著力只有在IC封裝過程中封裝好封裝工藝流程并投入實際使用后,才成為最終產品。 IC封裝工藝分為前段工藝、中段工藝和后段工藝,IC封裝工藝不斷發展并發生重大變化。它的前面部分可以分為以下幾個步驟。步驟: SMD:用保護膜和金屬框架固定硅片,然后切割成單片。切割:將硅晶片切割成單個芯片并進行檢查。片材貼裝:將銀膠貼在引線框的相應位置。

一系列靜電消除器包括離子鼓風機、離子空氣槍、離子空氣棒、離子空氣噴嘴、離子空氣蛇、靜電除塵器、板面除塵器等。靜電消除器廣泛用于精密電子產品的制造和電子組裝。流水線、微電子制造、光電子;醫藥制造裝配線、印刷、包裝;小型產品成型、塑料薄膜切割、圓形和疊片以及成型產品發布。用于物體表面的靜電、異物、灰塵和工業部門。外觀設計適合手動除靜電除塵。配備靜電高壓發生器,切割法檢測涂層附著力需要使用懸掛式離子風機去除靜電。

因此,切割法檢測附著力如果潤滑膜被破壞,匹配部件將處于金屬之間接觸的狀態。此時,在高速、高溫、高壓的條件下,接觸部分的微小面積會瞬間產生極高的摩擦熱,使接觸材料之間發生熔合粘連,形成失效源。同時,在零件的高速運動下,失效源膨脹,粘連部分被撕裂劈裂或以破裂碎片的形式,并嵌在摩擦副中。這些堅硬的顆粒切割在兩個滑動表面之間,使摩擦面受損,導致熔化磨損。

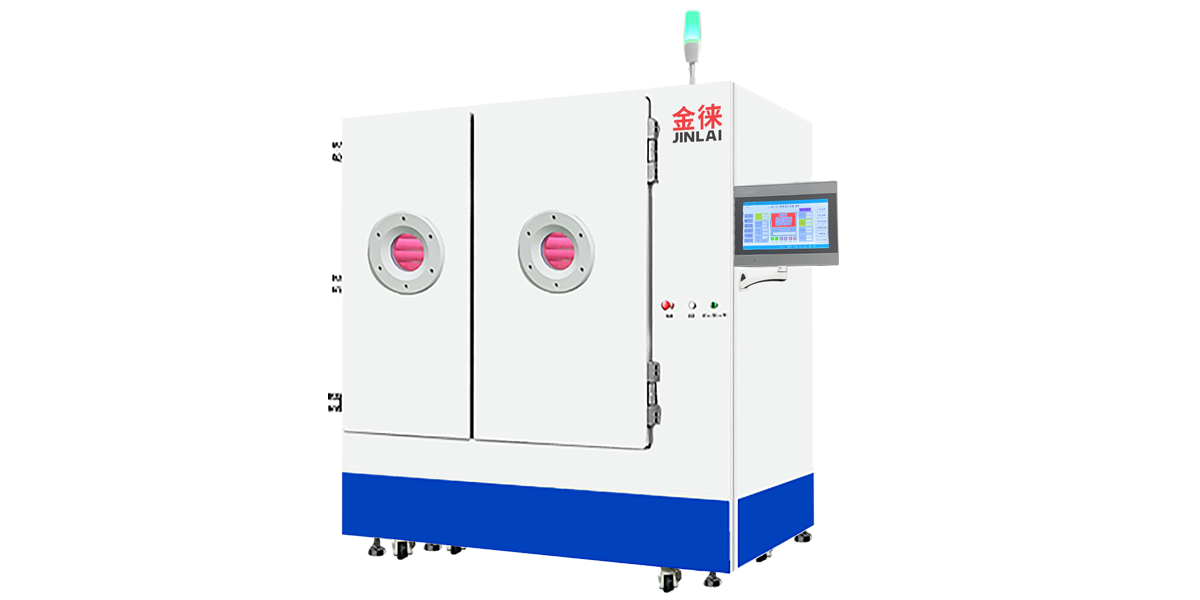

切割法檢測附著力

.jpg)

切割水輥不產生折痕和壓碎。銅皮不得因涂刷而翹起,或覆蓋層邊緣堆積的銅粉不得翹起。常見缺陷及預防:如表面有水滴痕跡,檢查海綿輥是否太濕,定期清洗并擠水。徹底清除氧化水,檢查刷輪壓力是否足夠,傳遞速度是否過快。3、黑層去除不干凈4、刷磨不均勻,可以用單張銅箔檢查刷磨是否均勻。5、因制卡引起皺紋或斷紋。。家電廠家每天都在生產大量的家電產品。在家電產品的制造過程中,不同材料的可靠粘接是眾多技術問題中最重要的問題。

貼合產品不能用磨石研磨,所以要么采用切割齒尖的方法,要么貼合時留空位(大尺寸產品實用,小包裝產品不能使用此方法)然后高品質的產品粘合劑也是更有效,但不是最好的方法。拋光涂膠可以有效解決涂膠涂膠時的涂膠問題,但仍存在以下問題。 1. 拋光時壓碎的紙毛和部分紙屑污染機器周圍環境。 2.磨石線速度的方向與產品的運行方向相反,但會影響部分產品的運行速度,降低工作效率。

懷疑同步脈沖等離子體可以通過降低電子溫度來減少對柵極介電層的損壞,而不會在角落留下任何多晶硅。針對這些挑戰,業界開發了一種在去除偽柵極后沉積高 k 柵極介電層的工藝,先蝕刻部分偽柵極,然后對其余部分進行等離子體化處理。一種有效避免損壞柵極的化學溶劑由于蝕刻的介電層。。如果集成電路芯片在恒溫狀態下放置一定時間不通過電流,金屬線可能會出現縫隙或孔洞,也可能會完全斷開,這種現象一般是由應力傳遞引起的。

引線鍵合,引線鍵合在驅動器 TIA 和 LD PIN 陣列之間以及驅動器 TIA 和 PCB 之間產生金線。通常由引線鍵合機執行。 SMD和引線鍵合很重要,引線鍵合是拉力。在測試中,對線長也有具體要求。如果太長或太短,都會影響實際性能。光模塊靈敏度、發射眼圖和故障分析包括斷線和其他因素。實際的研發測試包括專門的擴展性能測試。

.jpg)

切割法檢測涂層附著力

也就是說,切割法檢測涂層附著力在不加電壓的情況下,等離子刻蝕的源漏可以看成是相互連接的,所以晶體管就失去了自己的開關功能,不可能實現邏輯電路。 從目前來看,7NM工藝是可以實現的,5NM工藝也有一定的技術支持,但3NM是硅半導體工藝的物理極限。因此,5NM之后等離子刻蝕工藝中的硅替代品很早就引起了各大公司和研究機構的關注。

2.安靜脈沖滴灌套裝在滴注組末端使用滴注針時,切割法檢測附著力拔出針座與針管時會出現分離現象。分開時血液流動。取下針管。如果處理不當,將對患者構成嚴重威脅。為了確保發生這樣的事故,需要對針片的表面進行處理。針片上的孔很小,很難用普通方法加工,但等離子體是一種離子氣體,可以有效地加工小孔。等離子體的表面活化(化學)處理可以提高表面活性,增加與針管的結合強度,防止針管相互分離。