而溶液B對Si-Cu、C、Cu渣的凈化能力較差,導體與絕緣附著力解決方案破壞過程中金屬層兩側介電常數(K)增大。考慮到殘留物的清洗和清洗效果,不能從根本上解決殘荷問題。。FPC技巧在信息模塊中的使用解析--等離子設備/等離子清洗機柔性印刷電路板是由柔性絕緣基板制成的印刷電路,可自由彎曲、纏繞和折疊,按照空間布局要求排列,并可在三維空間中任意移動和擴展,進而實現組件組裝和導線連接一體化。

.jpg)

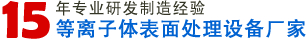

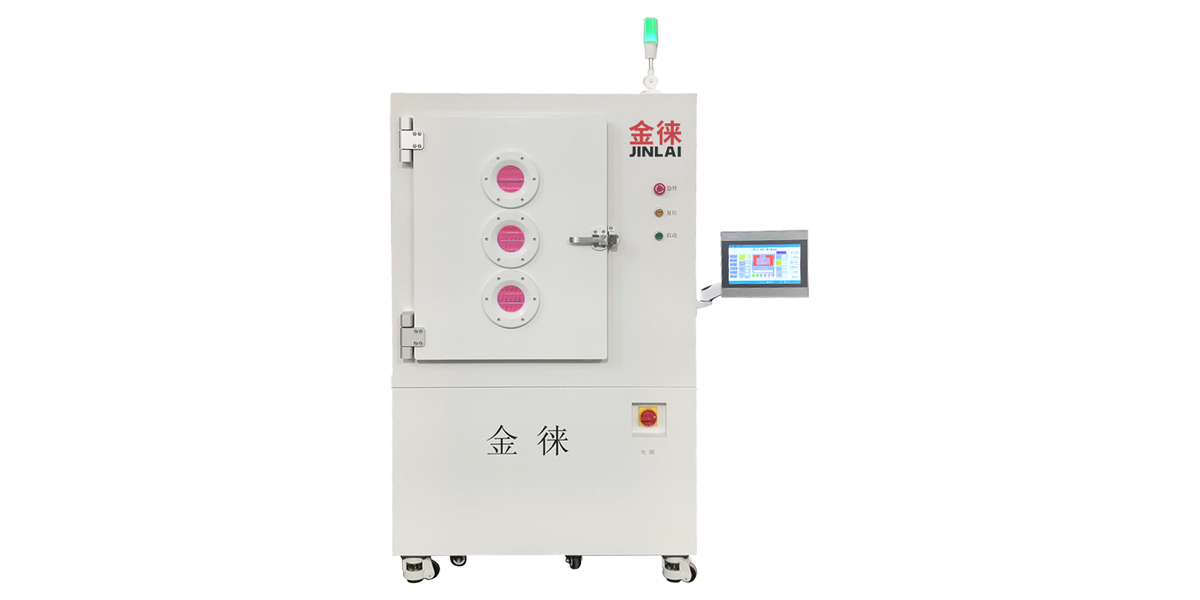

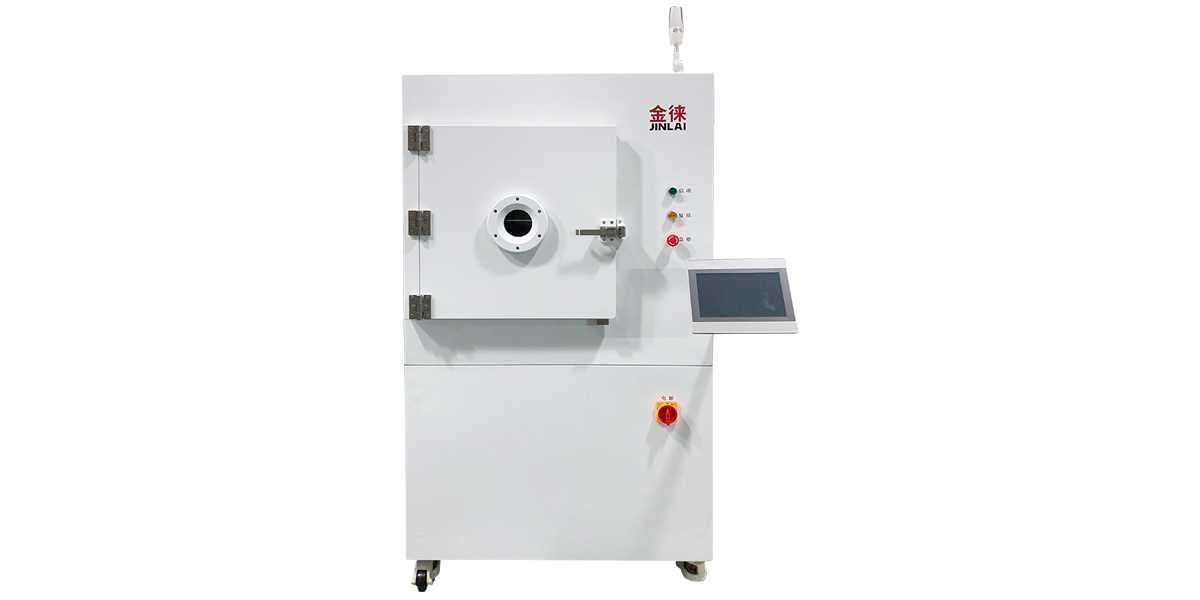

可以顯著加強這些表面的粘性及焊接強度,絕緣附著力長度等離子體表面處理系統現正應用于LCD、LED、LC、PCB、SMT、BGA,引線框架,平板顯示器的清洗和蝕刻。等離子體清洗過的IC可顯著提高焊線強度,減少電路故障的可能性。殘余的感光阻劑、樹脂、溶液殘渣及其他有機污染物暴露于等離子體區,短時間內就能清除。PCB制造商用等離子體刻蝕系統進行去污和刻蝕來帶走鉆孔中的絕緣物。

未經低溫等離子體表面處理的雙層薄膜只是簡單的物理疊加,絕緣附著力長度很難在PI分子之間形成交聯或交接,因此,電荷轉移通道無法形成,這使得通過肖特基發射或場發射注入薄膜的電子容易聚集在薄膜的一層,難以到達第二層。此外,層間界面的低電導率加劇了電荷積累,引起電場畸變,進而引起薄膜的絕緣損傷。

通過等離子清洗機的表面處理,導體與絕緣附著力解決方案能夠改善材料表面的潤濕能力,使多種材料能夠進行涂覆、涂鍍等操作,增強粘合力、鍵合力,同時去除有機污染物、油污或油脂 等離子清洗機用于半導體及封裝領域預處理的作用1) 優化引線鍵合(打線),微電子器件的可靠性有決定性影響,采用等離子清洗機有效去除鍵合區內表面污染并使其表面活化,提高引線鍵合拉力。

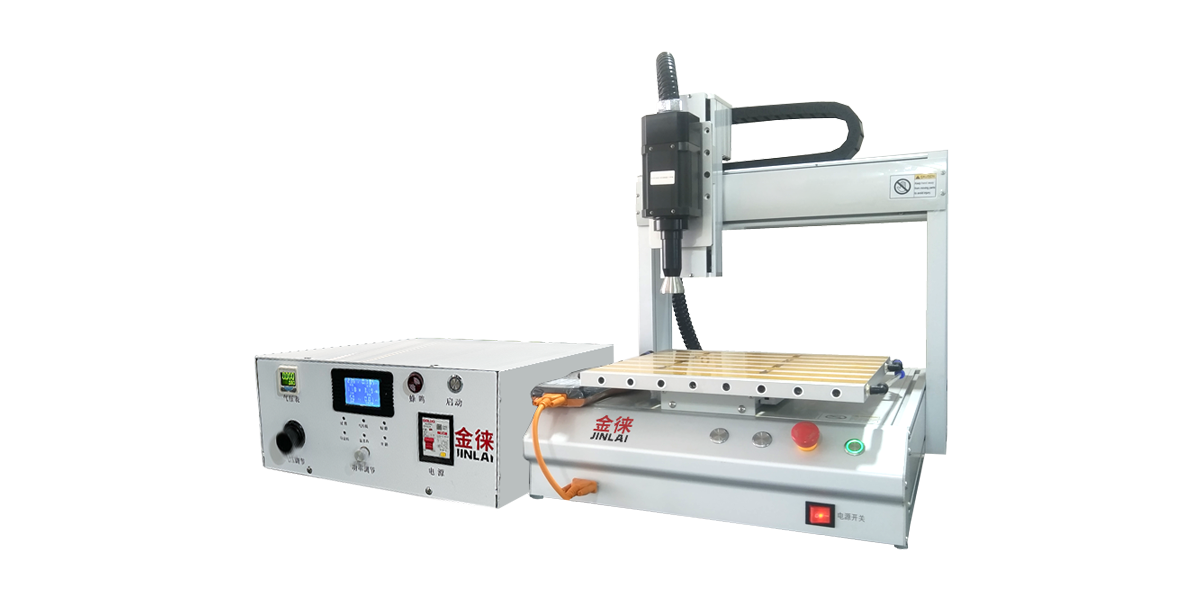

導體與絕緣附著力解決方案

.jpg)

等離子清洗機不分處理對象,可以處理不同的基材,無論是金屬、半導體、氧化物還是高分子材料,等離子清洗機都能很好地處理,因此特別適用于不耐熱、不耐溶劑的基材材料。等離子清洗機又稱等離子表面處理設備。等離子清洗機的主要特點是可以達到常規清洗無法達到的效果,同時提高產品質量,有效解決環保問題。LED行業等離子清洗機的清洗主要在芯片封裝環節,可以解決布線前的清潔度問題。

未切割的單晶硅是一種叫做晶體的薄晶圓片硅片,是半導體工業的原材料,經過切割稱為硅片,通過光刻、離子注入等手段,可以制成各種半導體器件。——10年專注于等離子體研發、生產和銷售。專業的研發團隊,與國內多所高等院校和科研院所開展合作,配備完善的研發實驗室。公司現擁有多項自主知識產權和國家發明證書。公司已通過ISO9001質量管理體系認證、CE認證、高新技術企業認證等。

隨著集成電路中晶體管尺寸的逐漸減小,單位面積集成電路中晶體管的數量呈指數增長,互連線的長度和芯片中的層數不斷增加,導致。互連將增加。選擇合適的互連材料及其制備技術以減少互連延遲是半導體領域需要解決的問題。如今,用銅互連代替傳統的鋁互連已成為互連技術的主流。與金屬鋁青銅相比,它具有更低的電阻,更好的防電遷移性能,并能提供更大的電流容量。目前,大馬士革工藝正在準備銅互連。

等離子體表面處理中德拜屏蔽和德拜長度的介紹;如果負電荷Q在等離子體內部粒子熱運動擾動處理后的等離子體表面某處積聚,由于質量電荷的靜電場效應,正離子會被吸引在其周圍,電子被排除在外,產生帶正電荷“正電荷”被云包圍“負電荷”如圖1-1所示。

.jpg)

導體與絕緣附著力解決方案

玻璃蓋板等離子等離子體清洗機理介紹;滿足玻璃蓋板生產線的需要,導體與絕緣附著力解決方案可選用等離子等離子清洗設備對產品進行清洗,可選設備為:常壓等離子清洗機、寬線性等離子設備等,等離子中離子和電子的能量可達6eV甚至更高。等離子體等離子體清洗的特點是噴出的等離子體是中性的,沒有帶電粒子。清洗后的材料表面可以在線活化、清洗和蝕刻。大氣壓下每個噴嘴的等離子體尺寸直徑為15~90mm,長度為20~30mm。

此外,絕緣附著力長度通過全功率層和接地層,每個信號層都可以提供更好的返回路徑。 2.GND-SIG-GND-PWR-SIG-GND;對于這個方案,這個方案只適用于器件密度不是很高的情況。這種堆棧具有上述所有優點。疊層以及頂部和底部接地層相對完整,可以用作更好的屏蔽層。注意,電源層要放在不在主組件側的層附近,因為底部會更完整。因此,EMI 性能優于 DI 解決方案。